### ST.ANNE'S

#### COLLEGE OF ENGINEERING AND TECHNOLOGY

(Approved by AICTE, New Delhi. Affiliated to Anna University, Chennai) (An ISO 9001: 2015 Certified Institution) ANGUCHETTYPALAYAM, PANRUTI – 607 106.

# DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

LAB MANUAL

JAN 2023- MAY 2023 / EVEN SEMESTER

**SUBJECT CODE/NAME:**

# EE3412/ LINEAR AND DIGITAL INTEGRATED CIRCUITS LABORATORY

**YEAR/SEM:** II/IV **BATCH**: 2021- 2025

AS PER ANNA UNIVERSITY, CHENNAI REGULATION 2021

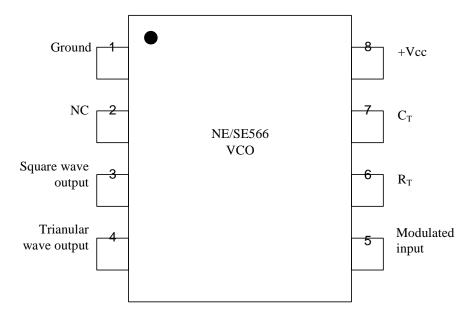

#### LIST OF EXPERIMENTS

- 1. Implementation of Boolean Functions, Adder and Subtractor circuits.

- 2. Code converters: Excess-3 to BCD and Binary to Gray code converter and viceversa

- 3. Parity generator and parity checking

- 4. Encoders and Decoders

- 5. Counters: Design and implementation of 3-bit modulo counters as synchronous and Asynchronous types using FF IC's and specific counter IC.

- 6. Shift Registers: Design and implementation of 4-bit shift registers in SISO, SIPO, PISO, PIPO modes using suitability IC's.

- 7. Study of multiplexer and de multiplexer

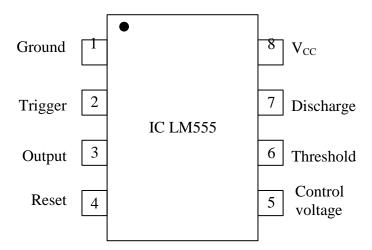

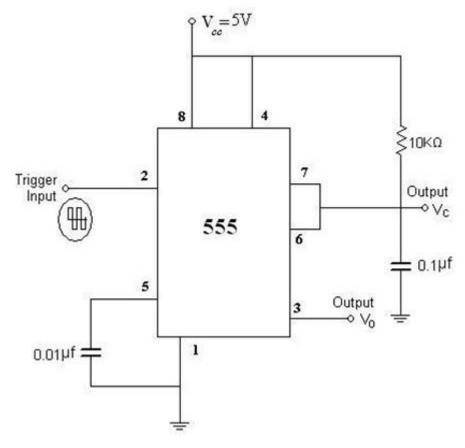

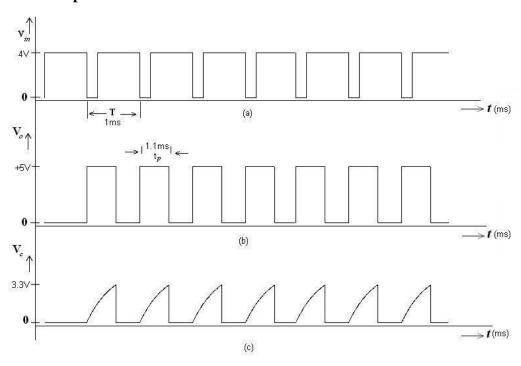

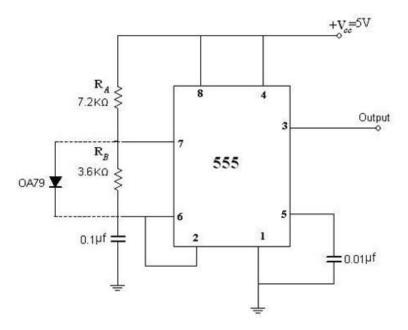

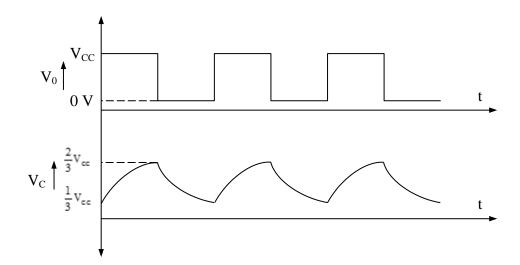

- 8. Timer IC application: Study of NE/SE 555 timer in Astability, Monostability operation.

- 9. Application of Op-Amp: inverting and non-inverting amplifier, Adder, comparator, Integrator and Differentiator.

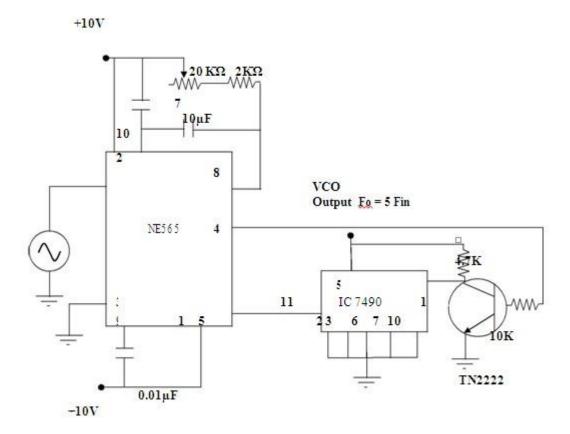

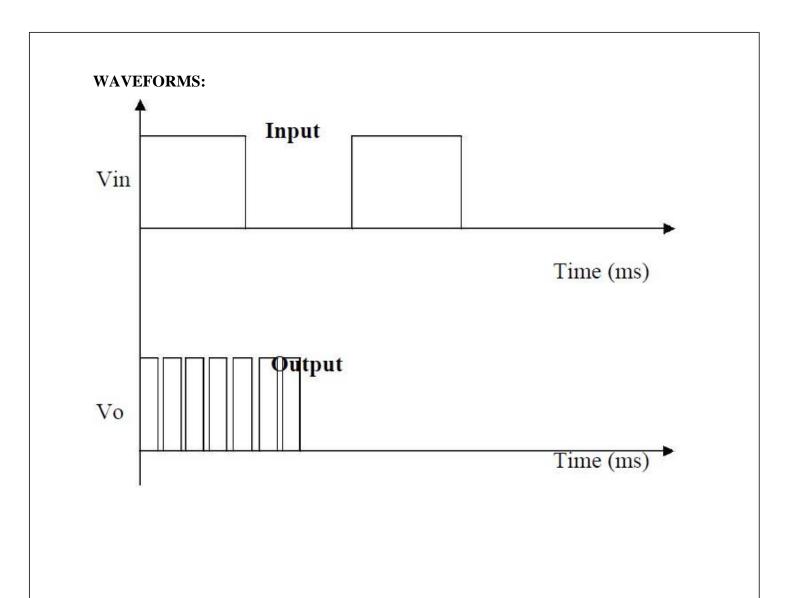

- 10. Voltage to frequency characteristics of NE/SE 566 IC.

- 11. Variability Voltage Regulator using IC LM317.

| Ex. | No.  | 1 |

|-----|------|---|

| D   | ate: |   |

#### IMPLEMENTATION OF BOOLEAN FUNCTIONS, ADDER / SUBTRACTOR CIRCUITS

#### **INTRODUCTION:**

#### HALF ADDER:

A combinational circuit which performs the addition of two bits is called half adder. The input variables designate the augend and the addend bit, whereas the output variables produce the sum and carry bits.

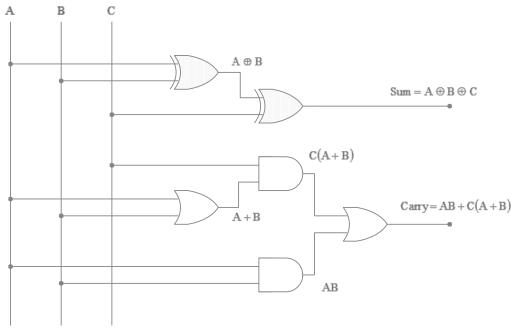

#### **FULL ADDER:**

A combinational circuit which performs the arithmetic sum of three input bits is called full adder. The three input bits include two significant bits and a previous carry bit. A full adder circuit can be implemented with two half adders and one OR gate.

#### HALF SUBTRACTOR:

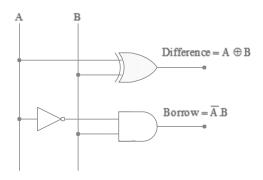

A combinational circuit which performs the subtraction of two bits is called half subtractor. The input variables designate the minuend and the subtrahend bit, whereas the output variables produce the difference and borrow bits.

#### **FULL SUBTRACTOR:**

A combinational circuit which performs the subtraction of three input bits is called full subtractor. The three input bits include two significant bits and a previous borrow bit. A full subtractor circuit can be implemented with two half subtractors and one OR gate.

#### ANNA UNIVERSITY QUESTIONS

- 1. Design and verify the truth table of a circuit which implements the following Boolean function  $F(A,B,C,D)=\sum m=(0,1,2,4,5,7,9,12,14)$  using logic gates. (100)

- 2. Simplify using K-map and implement using any suitable logic gates  $F(A,B,C,D) = \Sigma (3,4,5,7,9,13,14,15)$  (100)

- 3. Design and construct a half subtractor and full subtractor by using suitable logic gated and verify its truth table. (100)

- 4. Design and construct a half adder and full adder by using suitable logic gated and verify its truth table.

(100)

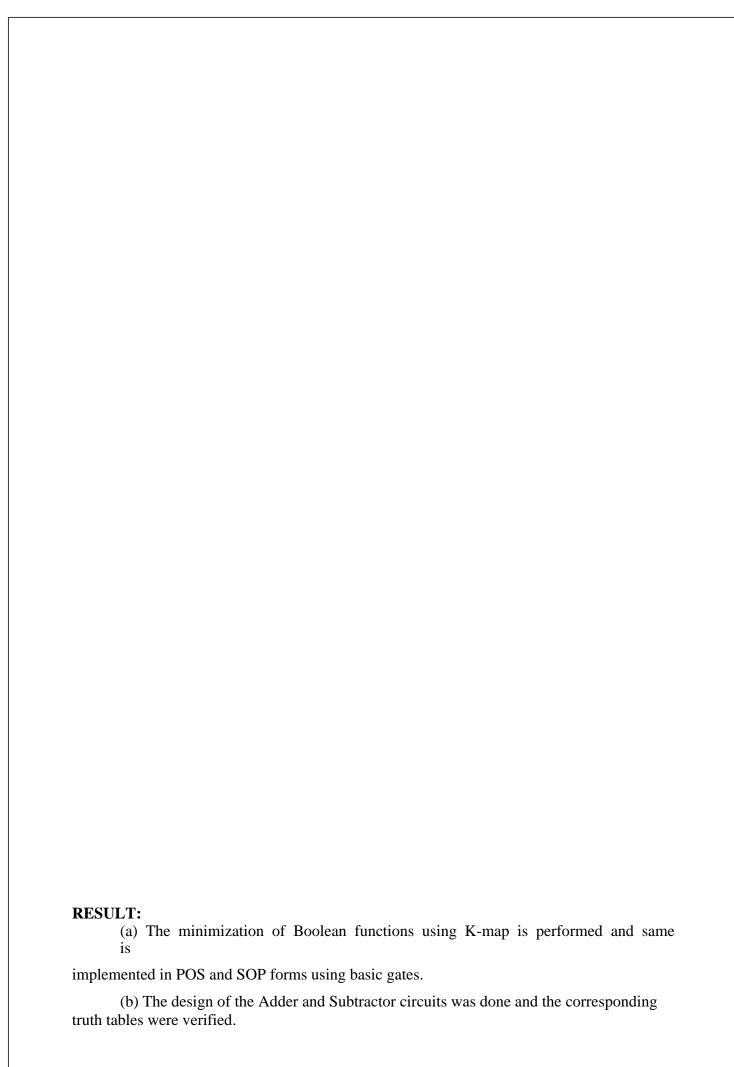

#### AIM:

- (a) To minimize Boolean functions using K-map and to implement the same in POS and SOP forms using basic gates.

- (b) To design and verify the truth table of the Adder & Subtractor circuits.

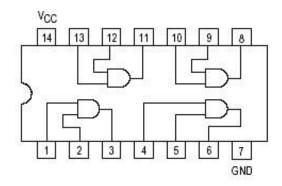

#### PIN DIAGRAM OF IC 7408:

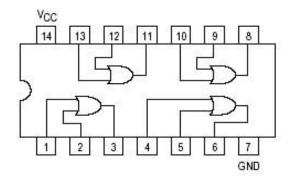

#### PIN DIAGRAM OF IC 7432:

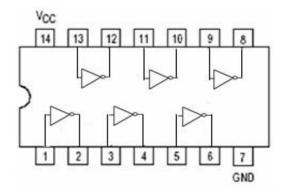

#### PIN DIAGRAM OF IC 7404:

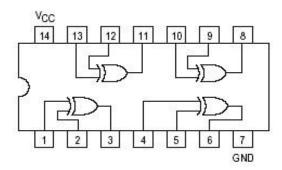

#### **PIN DIAGRAM OF IC 7486:**

#### **PRE-LAB QUESTIONS:**

1. In Boolean algebra the AND function is represented by the '+' sign

a). True

b). False

2. What is the most widely used method for the automated simplification of Boolean expressions?

a). Fast Fourier transforms

b). Quine-McCluskey minimisation

c). Binary reduction

d). Karnaugh maps

3. Physical logic gates take a finite time to respond to changes in their input signals.

What name is given to this time?

a). Propagation delay time

b). Rise time

c). Hold time

d). Set-up time

4. Express the binary number 1001 in decimal

a). 9

b). 11

c). 13

d). 15

5. Which of the following expressions is in the sum-of-products (SOP) form?

a). (A + B)(C + D)

b). (A)B (CD)

c). AB (CD)

d). AB + CD

#### **APPARATUS REQUIRED:**

| Sl.No | Component      | Specification | Quantity    |

|-------|----------------|---------------|-------------|

| 1     | AND GATE       | IC 7408       | 1           |

| 2     | X-OR GATE      | IC 7486       | 1           |

| 3     | NOT GATE       | IC 7404       | 1           |

| 4     | OR GATE        | IC 7432       | 1           |

| 5     | IC TRAINER KIT | -             | 1           |

| 6     | PATCH CORDS    | -             | As required |

#### **PROCEDURE:**

- 1. Connections are given as per the circuit diagrams.

- 2. For all the IC's 7<sup>th</sup> pin is grounded and 14<sup>th</sup> pin is connected to +5 V supply (V<sub>CC</sub>).

- 3. Apply the inputs and verify the truth table for the respective logic circuits.

# i. MINIMIZATION OF BOOLEAN FUNCTION IN SOP TRUTH TABLE – SOP:

|   | Input |   |   |   |  |

|---|-------|---|---|---|--|

| Α | В     | С | D | F |  |

| 0 | 0     | 0 | 0 | 0 |  |

| 0 | 0     | 0 | 1 | 0 |  |

| 0 | 0     | 1 | 0 | 1 |  |

| 0 | 0     | 1 | 1 | 1 |  |

| 0 | 1     | 0 | 0 | 0 |  |

| 0 | 1     | 0 | 1 | 1 |  |

| 0 | 1     | 1 | 0 | 0 |  |

| 0 | 1     | 1 | 1 | 1 |  |

| 1 | 0     | 0 | 0 | 0 |  |

| 1 | 0     | 0 | 1 | 1 |  |

| 1 | 0     | 1 | 0 | 0 |  |

| 1 | 0     | 1 | 1 | 1 |  |

| 1 | 1     | 0 | 0 | 1 |  |

| 1 | 1     | 0 | 1 | 1 |  |

| 1 | 1     | 1 | 0 | 1 |  |

| 1 | 1     | 1 | 1 | 0 |  |

#### **SUM OF PRODUCTS:**

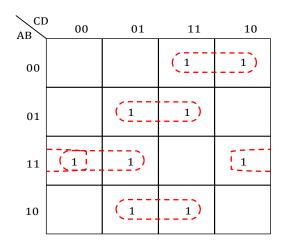

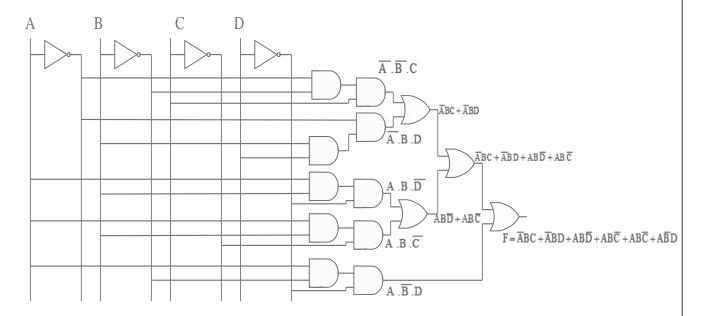

$F=\sum m (2, 3, 5, 7, 9, 11, 12, 13, 14)$

$F \cdot \overline{ABC} \cdot \overline{ABD} \cdot \overline{ABC} \cdot \overline{ABC} \cdot \overline{ABD}$

#### **LOGIC DIAGRAM – SOP:**

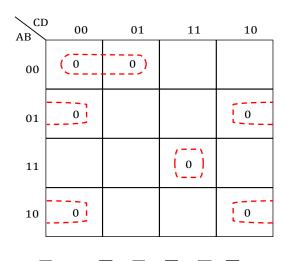

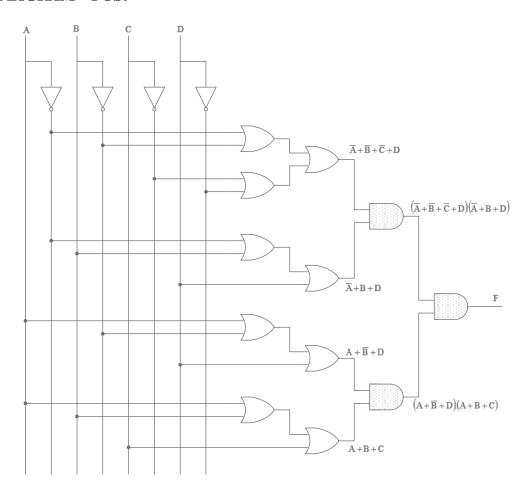

#### ii. PRODUCT OF SUMS:

#### **TRUTH TABLE – POS:**

|   | Inputs |   |   |   |  |  |

|---|--------|---|---|---|--|--|

| A | В      | С | D | F |  |  |

| 0 | 0      | 0 | 0 | 0 |  |  |

| 0 | 0      | 0 | 1 | 0 |  |  |

| 0 | 0      | 1 | 0 | 1 |  |  |

| 0 | 0      | 1 | 1 | 1 |  |  |

| 0 | 1      | 0 | 0 | 0 |  |  |

| 0 | 1      | 0 | 1 | 1 |  |  |

| 0 | 1      | 1 | 0 | 0 |  |  |

| 0 | 1      | 1 | 1 | 1 |  |  |

| 1 | 0      | 0 | 0 | 0 |  |  |

| 1 | 0      | 0 | 1 | 1 |  |  |

| 1 | 0      | 1 | 0 | 0 |  |  |

| 1 | 0      | 1 | 1 | 1 |  |  |

| 1 | 1      | 0 | 0 | 1 |  |  |

| 1 | 1      | 0 | 1 | 1 |  |  |

| 1 | 1      | 1 | 0 | 1 |  |  |

| 1 | 1      | 1 | 1 | 0 |  |  |

F · · · A · B · C · · · · A · B · D · · · A · B · C · D · · · A · B

#### **LOGIC DIAGRAM – POS:**

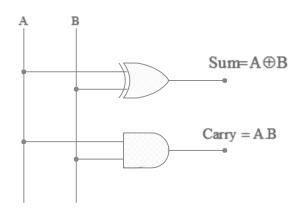

# IMPLEMENTATION OF HALF ADDER, FULL ADDER, HALF SUBTRACTOR AND FULL SUBTRACTOR CIRCUITS:

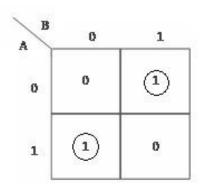

#### **HALF ADDER:**

#### **TRUTH TABLE:**

| Inputs |   | Output   |   |  |

|--------|---|----------|---|--|

| A      | В | Sum Carı |   |  |

| 0      | 0 | 0        | 0 |  |

| 0      | 1 | 1        | 0 |  |

| 1      | 0 | 1        | 0 |  |

| 1      | 1 | 0        | 1 |  |

#### **DESIGN:**

From the truth table the expression for sum and carry bits of the output can be obtained as,

Sum,

$$S = A \oplus B$$

Carry,

$$C = A \cdot B$$

#### SUM:

$$Sum = (A.\overline{B} \cdot \overline{A}B) \cdot A$$

$$\cdot B$$

#### **CARRY:**

#### LOGIC DIAGRAM OF HALF ADDER:

### **FULL ADDER:** TRUTH TABLE:

|   | Inputs |   |          | put |  |

|---|--------|---|----------|-----|--|

| A | В      | С | Sum Carr |     |  |

| 0 | 0      | 0 | 0        | 0   |  |

| 0 | 0      | 1 | 1        | 0   |  |

| 0 | 1      | 0 | 1        | 0   |  |

| 0 | 1      | 1 | 0        | 1   |  |

| 1 | 0      | 0 | 1        | 0   |  |

| 1 | 0      | 1 | 0        | 1   |  |

| 1 | 1      | 0 | 0        | 1   |  |

| 1 | 1      | 1 | 1        | 1   |  |

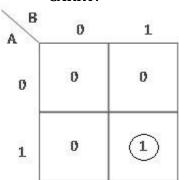

#### **DESIGN:**

From the truth table the expression for sum and carry bits of the output can be obtained as,

$$SUM = A'B'C + A'BC' + AB'C' + ABC$$

$$CARRY = A'BC + AB'C + ABC' + ABC$$

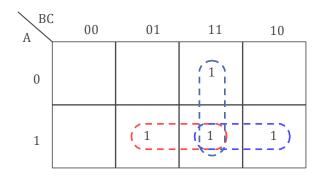

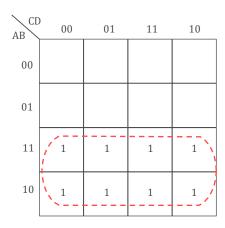

Using Karnaugh maps the reduced expression for the output bits can be obtained as,

#### **SUM**

#### **CARRY**

CARRY = AB + AC + BC

#### LOGIC DIAGRAM OF FULL ADDER:

#### **HALF SUBTRACTOR:**

#### **TRUTH TABLE:**

| Inputs |   | Output     |        |  |

|--------|---|------------|--------|--|

| A      | В | Difference | Borrow |  |

| 0      | 0 | 0          | 0      |  |

| 0      | 1 | 1          | 1      |  |

| 1      | 0 | 1          | 0      |  |

| 1      | 1 | 0          | 0      |  |

#### **DESIGN:**

From the truth table the expression for difference and borrow bits of the output can be obtained as,

Difference, DIFF =  $A \oplus B$ Borrow, BORR = A'. B

#### LOGIC DIAGRAM OF HALF SUBTRACTOR:

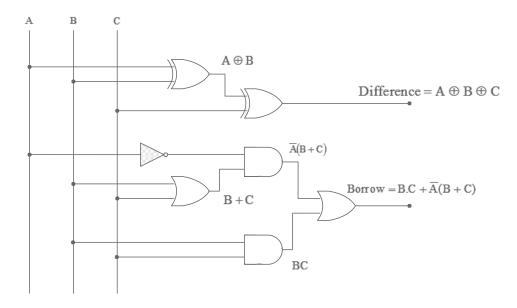

#### **FULL SUBTRACTOR:**

#### **TRUTH TABLE:**

| Inputs |   |   | Output     |        |  |

|--------|---|---|------------|--------|--|

| A      | В | C | Difference | Borrow |  |

| 0      | 0 | 0 | 0          | 0      |  |

| 0      | 0 | 1 | 1          | 1      |  |

| 0      | 1 | 0 | 1          | 1      |  |

| 0      | 1 | 1 | 0          | 1      |  |

| 1      | 0 | 0 | 1          | 0      |  |

| 1      | 0 | 1 | 0          | 0      |  |

| 1      | 1 | 0 | 0          | 0      |  |

| 1      | 1 | 1 | 1          | 1      |  |

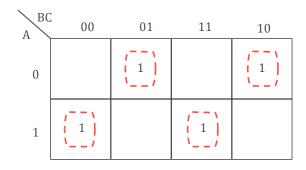

#### **DESIGN:**

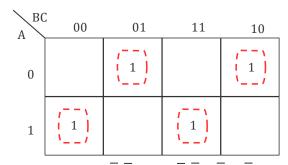

From the truth table the expression for difference and borrow bits of the output can be obtained as,

Difference= A'B'C + A'BC' + AB'C' + ABC

Borrow = A'BC + AB'C + ABC' + ABC

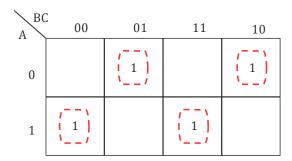

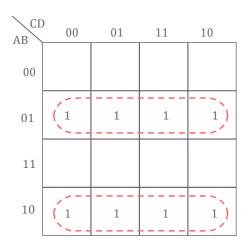

Using Karnaugh maps the reduced expression for the output bits can be obtained as,

#### **DIFFERENCE**

DIFFERENCE ·  $(A.B.C \cdot A.B.C \cdot A.B.C \cdot A.B.C)$

$\cdot A \cdot B \cdot C$

#### **BORROW**

BORROW ·  $B.C \cdot A(B \cdot C)$

#### LOGIC DIAGRAM OF FULL SUBTRACTOR:

#### **VIVA QUESTIONS:**

- 1. What are the associative laws of Boolean algebra?

- 2. Why NAND and NOR are called Universal Gates?

- 3. What is meant by sum of product form?

- 4. What is the use of a full adder circuit?

- 5. What is a subtractor?

#### **POST-LAB QUESTIONS:**

| 1. | Half-adders    | can be c | combined to | o form a | full-adder | with no | additional | gates. |

|----|----------------|----------|-------------|----------|------------|---------|------------|--------|

|    | 110011 0000010 |          |             |          | 1011 00001 |         |            | 5      |

a). True

b). False

2. A full-adder adds \_\_\_\_\_.

a). two single bits and one carry bit

b). two 2-bit binary numbers

c). two 4-bit binary numbers

d). two 2-bit numbers and one carry bit

$$ACD + ABC + ABCD$$

.

a).

$$F = ABD + ABC + CD$$

b).

$$F = CD + AD$$

c).

$$F = BC + AB$$

d).

$$F = AC + AD$$

4. Fast-look-ahead carry circuits found in most 4-bit full-adder circuits:

a). determine sign and magnitude

b). Reduce propagation delay

c). add a 1 to complemented inputs

d). Increase ripple delay

5. Why is a fast-look-ahead carry circuit used in the 7483 4-bit full-adder?

a). to decrease the cost

b). To make it smaller

c). to slow down the circuit

d). To speed up the circuit

| Ex. No. 2 |                 |

|-----------|-----------------|

|           | CODE CONVERTERS |

| Date:     |                 |

|           |                 |

#### **INTRODUCTION:**

Code converter is a circuit that makes two systems compatible even though each uses different binary codes. There is a wide variety of binary codes used in digital systems. Some of these codes are Binary Coded Decimal, Gray code, Excess- 3 code, ASCII code, etc.

#### ANNA UNIVERSITY QUESTIONS

- 1. Design a 3 bit binary to gray code converter and verify its truth table. (50)

- 2. Design a gray to binary code converter using suitable logic gates and verify their function.

(50)

- 3. Design and construct binary to gray code converter and gray to binary code converter by using suitable logic gated and verify its truth table. (100)

- 4. Design and construct BCD to Excess-3code converter by using suitable logic gated

and verify its truth table.

5. Design and construct Excess-3 to BCD code converter by using suitable logic gated and verify its truth table. (100)

(100)

#### AIM:

To construct logic diagram and to verify the truth table for,

- (a) Excess-3 to BCD code converter

- (b) BCD to Excess-3 code converter

- (c) Binary to Gray code Converter

- (d) Gray to Binary code converter

#### **EXCESS -3 TO BCD CONVERTER:**

#### **TRUTH TABLE:**

| Excess – 3 input |   |   |   | BCD ou | ıtput |    |    |

|------------------|---|---|---|--------|-------|----|----|

| A                | В | С | D | В3     | B2    | B1 | В0 |

| 0                | 0 | 1 | 1 | 0      | 0     | 0  | 0  |

| 0                | 1 | 0 | 0 | 0      | 0     | 0  | 1  |

| 0                | 1 | 0 | 1 | 0      | 0     | 1  | 0  |

| 0                | 1 | 1 | 0 | 0      | 0     | 1  | 1  |

| 0                | 1 | 1 | 1 | 0      | 1     | 0  | 0  |

| 1                | 0 | 0 | 0 | 0      | 1     | 0  | 1  |

| 1                | 0 | 0 | 1 | 0      | 1     | 1  | 0  |

| 1                | 0 | 1 | 0 | 0      | 1     | 1  | 1  |

| 1                | 0 | 1 | 1 | 1      | 0     | 0  | 0  |

| 1                | 1 | 0 | 0 | 1      | 0     | 0  | 1  |

#### PRE-LAB QUESTIONS

1. How many outputs are on a BCD decoder?

a). 4

b). 16

c). 8

d). 10

2. The expansion inputs to a comparator are used for expansion to a(n):

a). 4-bit system

b). 8-bit system

c). BCD system

d).Counter system

3. A BCD decoder will have how many rows in its truth table?

a). 10

b). 9

c). 8

d). 3

4. A binary code that progresses such that only one bit changes between two successive codes is:

a). nine's-complement code

b). 8421 code

c). excess-3 code

d). Gray code

5. Which type of error is eliminated through the use of the Gray code?

a). decoding

b). timing

c). encoding

d). conversion

#### **APPARATUS REQUIRED:**

| Sl.No | Component      | Specification | Quantity    |

|-------|----------------|---------------|-------------|

| 1     | AND GATE       | IC 7408       | 1           |

| 2     | X-OR GATE      | IC 7486       | 1           |

| 3     | NOT GATE       | IC 7404       | 1           |

| 4     | OR GATE        | IC 7432       | 1           |

| 5     | IC TRAINER KIT | -             | 1           |

| 6     | PATCH CORDS    | -             | As required |

#### **PROCEDURE:**

- The logic circuit is designed using K map.

- · Gates are decided for the logic circuit.

- · Connections are made as per the logic diagrams.

- · Truth tables are verified.

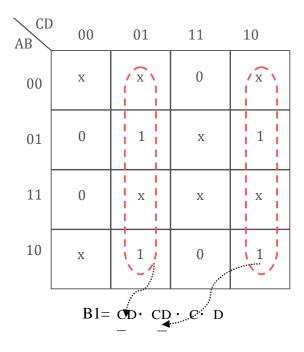

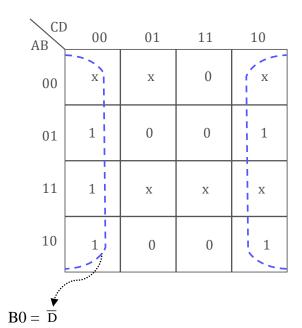

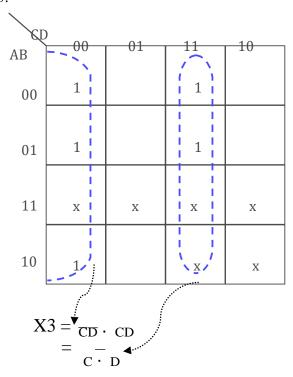

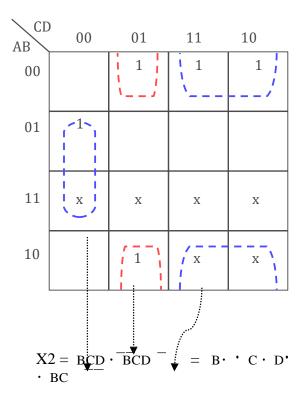

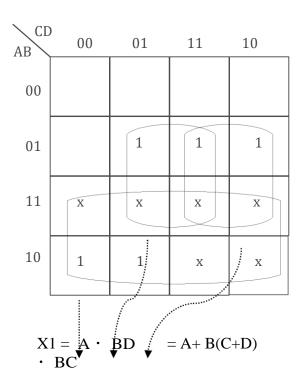

#### K- MAP: EXCESS - 3 TO BCD

B3:

| AB CD | 00 | 01        | 11        | 10     |

|-------|----|-----------|-----------|--------|

| 00    |    |           | 0         |        |

| 01    | 0  | 0         | 0         | 0      |

| 11    |    | Х         | X   X     | x )    |

| 10    | 0  | 0         | 1,        | 0      |

|       |    | B3 = AB - | + ABC = A | (B+BC) |

B2:

B1:

B0:

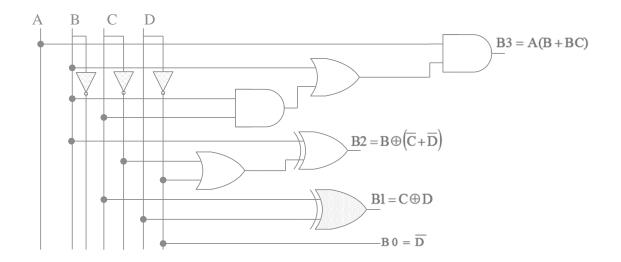

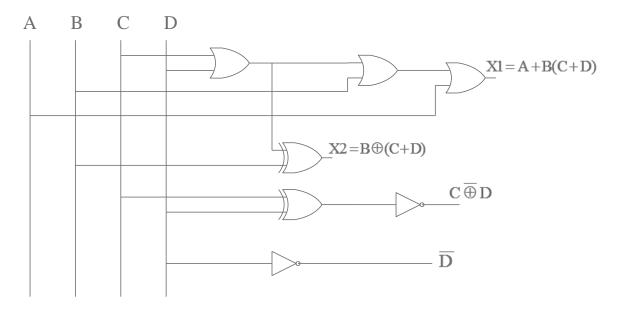

#### LOGIC DIAGRAM OF EXCESS – 3 TO BCD CONVERSION

#### **BCD TO EXCESS -3 CONVERTER:**

#### **TRUTH TABLE:**

| BCD input |   |   |   | Excess – 3 output |    |    |    |  |

|-----------|---|---|---|-------------------|----|----|----|--|

| A         | В | С | D | X1                | X2 | Х3 | X4 |  |

| 0         | 0 | 0 | 0 | 0                 | 0  | 1  | 1  |  |

| 0         | 0 | 0 | 1 | 0                 | 1  | 0  | 0  |  |

| 0         | 0 | 1 | 0 | 0                 | 1  | 0  | 1  |  |

| 0         | 0 | 1 | 1 | 0                 | 1  | 1  | 0  |  |

| 0         | 1 | 0 | 0 | 0                 | 1  | 1  | 1  |  |

| 0         | 1 | 0 | 1 | 1                 | 0  | 0  | 0  |  |

| 0         | 1 | 1 | 0 | 1                 | 0  | 0  | 1  |  |

| 0         | 1 | 1 | 1 | 1                 | 0  | 1  | 0  |  |

| 1         | 0 | 0 | 0 | 1                 | 0  | 1  | 1  |  |

| 1         | 0 | 0 | 1 | 1                 | 1  | 0  | 0  |  |

| 1         | 0 | 1 | 0 | X                 | X  | X  | X  |  |

| 1         | 0 | 1 | 1 | X                 | X  | X  | X  |  |

| 1         | 1 | 0 | 0 | X                 | X  | X  | X  |  |

| 1         | 1 | 0 | 1 | X                 | X  | X  | X  |  |

| 1         | 1 | 1 | 0 | X                 | X  | X  | X  |  |

| 1         | 1 | 1 | 1 | X                 | X  | X  | X  |  |

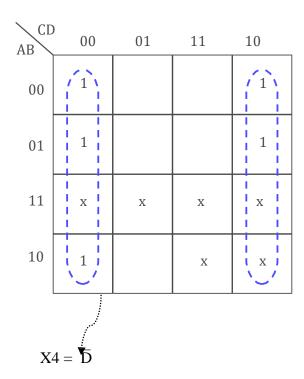

X4:

X3:

X2:

X1:

#### **LOGIC DIAGRAM:**

#### BINARY TO GRAY CODE CONVERTER

#### **TRUTH TABLE:**

| <b>B</b> 0 | C             | D                       | 01                                                                                                                |                                                                                                                                                       |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                     |

|------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          |               |                         | G1                                                                                                                | G2                                                                                                                                                    | G3                                                                                                                                                                                        | G4                                                                                                                                                                                                                                                                                                  |

|            | 0             | 0                       | 0                                                                                                                 | 0                                                                                                                                                     | 0                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   |

| 0          | 0             | 1                       | 0                                                                                                                 | 0                                                                                                                                                     | 0                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                   |

| 0          | 1             | 0                       | 0                                                                                                                 | 0                                                                                                                                                     | 1                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                   |

| 0          | 1             | 1                       | 0                                                                                                                 | 0                                                                                                                                                     | 1                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   |

| 1          | 0             | 0                       | 0                                                                                                                 | 1                                                                                                                                                     | 1                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   |

| 1          | 0             | 1                       | 0                                                                                                                 | 1                                                                                                                                                     | 1                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                   |

| 1          | 1             | 0                       | 0                                                                                                                 | 1                                                                                                                                                     | 0                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                   |

| 1          | 1             | 1                       | 0                                                                                                                 | 1                                                                                                                                                     | 0                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   |

| 0          | 0             | 0                       | 1                                                                                                                 | 1                                                                                                                                                     | 0                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   |

|            | 0 0 1 1 1 1 1 | 0 1 0 1 1 0 1 1 1 1 1 1 | 0     1     0       0     1     1       1     0     0       1     0     1       1     1     0       1     1     1 | 0     1     0     0       0     1     1     0       1     0     0     0       1     0     1     0       1     1     0     0       1     1     1     0 | 0     1     0     0     0       0     1     1     0     0       1     0     0     0     1       1     0     1     0     1       1     1     0     0     1       1     1     1     0     1 | 0       1       0       0       0       1         0       1       1       0       0       1         1       0       0       0       1       1         1       0       1       0       1       0         1       1       1       0       1       0         1       1       1       0       1       0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

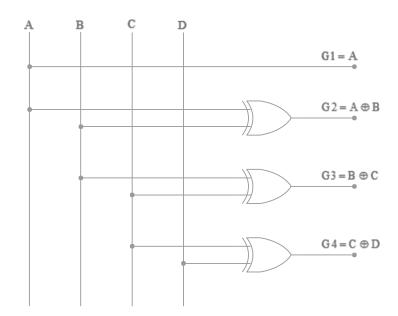

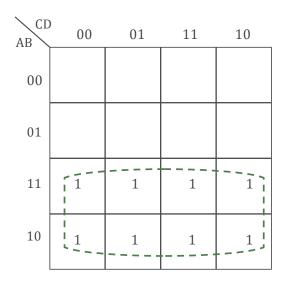

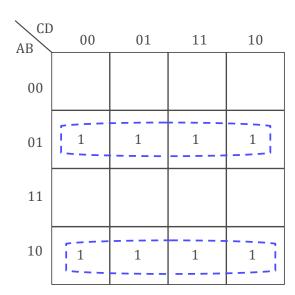

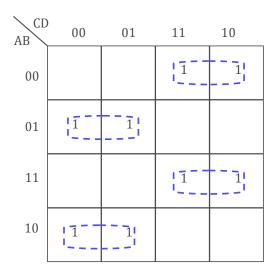

#### K- MAP: **BINARY TO GRAY**

G1:

G1 = A

G2:

$G2 \cdot \overline{A}.B \cdot \overline{A}.B \cdot A \cdot B$

G3:

G4:

$G4 \cdot \overline{C}.D \cdot \overline{C}.D \cdot C \cdot D$

#### **LOGIC DIAGRAM:**

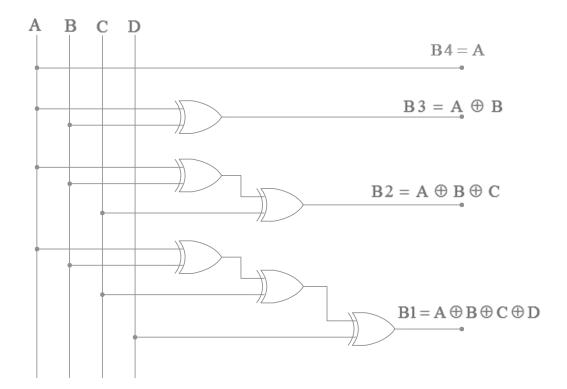

#### **GRAY TO BINARY CODE CONVERTER:**

#### TRUTH TABLE:

| GRAY CODE |   |   |   | BINARY CODE |    |    |    |  |

|-----------|---|---|---|-------------|----|----|----|--|

| A         | В | С | D | B1          | B2 | В3 | B4 |  |

| 0         | 0 | 0 | 0 | 0           | 0  | 0  | 0  |  |

| 0         | 0 | 0 | 1 | 0           | 0  | 0  | 1  |  |

| 0         | 0 | 1 | 0 | 0           | 0  | 1  | 1  |  |

| 0         | 0 | 1 | 1 | 0           | 0  | 1  | 0  |  |

| 0         | 1 | 0 | 0 | 0           | 1  | 1  | 0  |  |

| 0         | 1 | 0 | 1 | 0           | 1  | 1  | 1  |  |

| 0         | 1 | 1 | 0 | 0           | 1  | 0  | 1  |  |

| 0         | 1 | 1 | 1 | 0           | 1  | 0  | 0  |  |

| 1         | 0 | 0 | 0 | 1           | 1  | 1  | 0  |  |

| 1         | 0 | 0 | 1 | 1           | 1  | 1  | 1  |  |

| 1         | 0 | 1 | 0 | 1           | 1  | 0  | 1  |  |

| 1         | 0 | 1 | 1 | 1           | 1  | 0  | 0  |  |

| 1         | 1 | 0 | 0 | 1           | 0  | 0  | 0  |  |

| 1         | 1 | 0 | 1 | 1           | 0  | 0  | 1  |  |

| 1         | 1 | 1 | 0 | 1           | 0  | 1  | 1  |  |

| 1         | 1 | 1 | 1 | 1           | 0  | 1  | 0  |  |

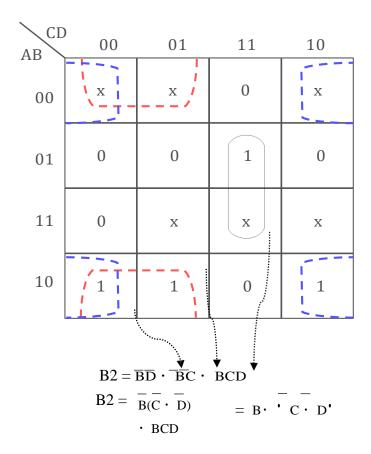

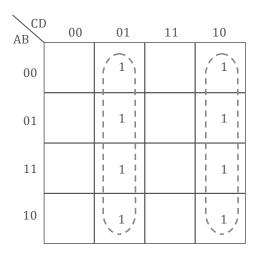

K-MAP: B1:

B1 = A

B2:

$B2 = \overline{AB} \cdot \overline{AB} \cdot A \cdot B$

B3:

$$B3 = \overline{ABC} \cdot \overline{ABC} \cdot \overline{ABC} = A \cdot B \cdot C$$

$$\cdot ABC$$

B4:

| AB | 00                                                       | 01  | 11 | 10 |

|----|----------------------------------------------------------|-----|----|----|

| 00 |                                                          | [1] |    |    |

| 01 | $\left[\begin{array}{c} \overline{1} \end{array}\right]$ |     |    |    |

| 11 |                                                          |     |    |    |

| 10 |                                                          |     |    |    |

$$B4 = A \cdot B \cdot C \cdot D$$

### **LOGIC DIAGRAM:**

# **VIVA QUESTIONS:**

- 1. What is the need for code converters?

- 2. Convert 10002 into Gray code and Excess 3 code.

- 3. Mention the rules for Gray to Binary code conversion.

- 4. Convert (367)<sub>10</sub> into Excess 3 code.

- 5. Convert the Gray coded number 10011011 to its binary equivalent.

### **POST-LAB QUESTIONS:**

- 1. One use for Gray code is:

- a). coded representation of a shaft's mechanical position

- b). turning on/off software switches

- c). to represent the correct ASCII code to indicate the position of machinery

- d). to convert the angular position of machinery into hexadecimal code

- 2. Which of the following is not a weighted value positional numbering system:

- a). hexadecimal

b). Binary-coded decimal

c). binary

- d). Octal

- 3. Use the weighting factors to convert the following BCD numbers to binary: 0101

- 0011 0010 0110 1000

- a). 01010011 001001101000

- b). 11010100 100001100000

- c). 110101

- 100001100

- d). 101011

- 001100001

- 4. In a BCD-to-seven-segment converter, why must a code converter be utilized?

- a). to convert the 4-bit BCD into 7-bit code

- b). to convert the 4-bit BCD into 10-bit code

- c). to convert the 4-bit BCD into Gray code

- d). No conversion is necessary.

- 5. One way to convert BCD to binary using the hardware approach is:

- a). with MSI IC circuits

b). With a keyboard encoder

c). with an ALU

d). UART

#### **RESULT:**

Thus the logic diagrams are constructed and truth tables are verified for,

- (a) Excess-3 to BCD

- (b) BCD to Excess-3

- (c) Binary to Gray code Converter

- (d) Gray to Binary code converter

Ex. No. 3

PARITY GENERATOR AND PARITY CHECKER

Date:

#### **INTRODUCTION:**

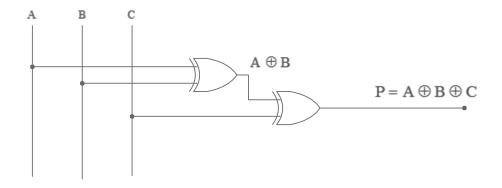

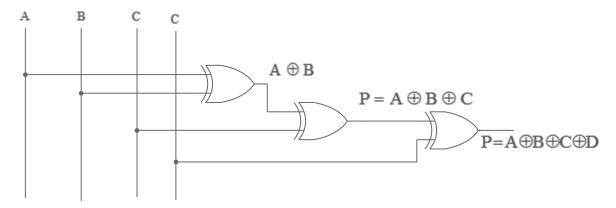

A parity bit is used for the purpose of detecting errors during transmission of binary information. A parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message including the parity bit is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator and the circuit that checks the parity in the receiver is called a parity checker.

### **ANNA UNIVERSITY QUESTIONS**

1. Design and construct a three bit odd and even parity generator and checker using basic gates.

(100)

- 2. Design the logic circuit for the 4-bit odd parity generator and checker. (50)

- 3. Design the logic circuit for the 4-bit even parity generator and checker. (50)

- 4. Design and verify the truth table of a circuit which generates odd parity bit for three bit binary input. (50)

- 5. Design and verify the truth table of a circuit which generates even parity bit for three bit binary input. (50)

#### AIM:

To construct logic circuit and to verify the truth table for:

- (a) Odd Parity Generator

- (b) Odd Parity Checker

- (c) Even Parity Generator

- (d) Even Parity Checker

#### **ODD PARITY GENERATOR:**

### **TRUTH TABLE:**

| INPUT |   |   | OUTPUT |

|-------|---|---|--------|

| A     | В | C | P      |

| 0     | 0 | 0 | 1      |

| 0 | 0 | 1 | 0 |

|---|---|---|---|

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

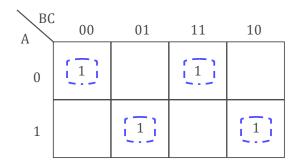

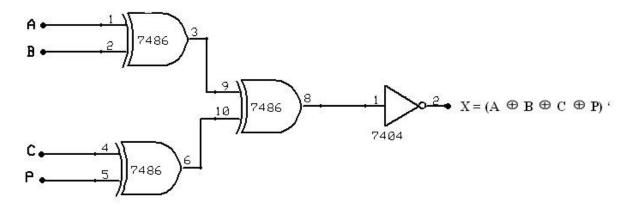

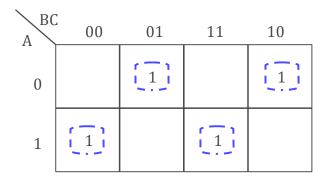

# K-MAP: ODD PARITY GENERATOR:

$P = \cdot A \cdot B \cdot C + \cdot ABC + A \cdot BC + AB \cdot C$

$P = \overline{A} \cdot \overline{B} \cdot \overline{C}$

## **LOGIC DIAGRAM:**

## **ODD PARITY CHECKER:**

## **TRUTH TABLE:**

| INPUT |   |   |      | OUTPUT |

|-------|---|---|------|--------|

| A     | В | С | D(P) | P      |

| 0     | 0 | 0 | 0    | 1      |

| 0     | 0 | 0 | 1    | 0      |

| 0     | 0 | 1 | 0    | 0      |

| 0     | 0 | 1 | 1    | 1      |

| 0     | 1 | 0 | 0    | 0      |

| 0     | 1 | 0 | 1    | 1      |

| 0     | 1 | 1 | 0    | 1      |

| 0     | 1 | 1 | 1    | 0      |

| 1     | 0 | 0 | 0    | 0      |

| 1     | 0 | 0 | 1    | 1      |

| 1     | 0 | 1 | 0    | 1      |

| 1     | 0 | 1 | 1    | 0      |

| 1     | 1 | 0 | 0    | 1      |

| 1     | 1 | 0 | 1    | 0      |

| 1     | 1 | 1 | 0    | 0      |

| 1     | 1 | 1 | 1    | 1      |

# K-MAP: ODD PARITY CHECKER

| AB | 00                                           | 01 | 11             | 10 |

|----|----------------------------------------------|----|----------------|----|

| 00 | [1]                                          |    | $\binom{1}{1}$ |    |

| 01 |                                              |    |                |    |

| 11 | $\begin{bmatrix} \overline{1} \end{bmatrix}$ |    |                |    |

| 10 |                                              |    |                |    |

$$X = A \cdot B \cdot C \cdot P'$$

# PRE-LAB QUESTIONS

| 1. | What is an important attribute of the   | ne conditional signal assignment statement?    |

|----|-----------------------------------------|------------------------------------------------|

|    | a). Its tristate outputs                | b). Its sequential evaluation                  |

|    | c). its use of library components       | d). Its fast activation times                  |

| 2. | A simple parity-check code can de       | tect errors.                                   |

|    | a). an even-number of                   | b). Two                                        |

|    | c). no errors                           | d). an odd-number of                           |

| 3. | The Hamming distance between eq         | qual code words is                             |

|    | a). 1                                   | b). n                                          |

|    | c). 0                                   | d). None                                       |

| 4. | The divisor in a cyclic code is norr    | mally called the                               |

|    | a). Degree                              | b). Generator                                  |

|    | c). Redundancy                          | d). None                                       |

| 5. | In block coding, if $n = 5$ , the maxim | mum Hamming distance between two code words is |

|    | ·                                       |                                                |

|    | a). 2                                   | b). 3                                          |

|    | c). 5                                   | d). None                                       |

## **APPARATUS REQUIRED:**

| Sl.No | Component      | Specification | Quantity    |

|-------|----------------|---------------|-------------|

| 1     | X-OR GATE      | IC 7486       | 1           |

| 2     | NOT GATE       | IC 7404       | 1           |

| 3     | IC TRAINER KIT | -             | 1           |

| 4     | PATCH CORDS    | -             | As required |

### **PROCEDURE:**

- The logic circuit is designed using K map.

- · Gates are decided for the logic circuit.

- · Connections are made as per the logic diagrams.

- · Apply the inputs and verify the truth table for the Parity generator and checker.

## **ODD PARITY CHECKER**

### **EVEN PARITY GENERATOR:**

### **TRUTH TABLE:**

|   | INPUT | OUTPUT |   |

|---|-------|--------|---|

| A | В     | C      | P |

| 0 | 0     | 0      | 0 |

| 0 | 0     | 1      | 1 |

| 0 | 1     | 0      | 1 |

| 0 | 1     | 1      | 0 |

| 1 | 0     | 0      | 1 |

| 1 | 0     | 1      | 0 |

| 1 | 1     | 0      | 0 |

| 1 | 1     | 1      | 1 |

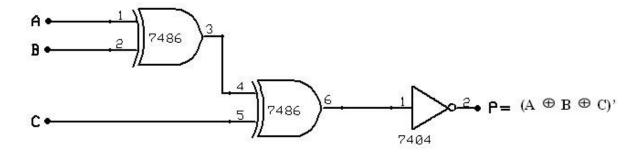

### K-MAP: EVEN PARITY GENERATOR

$$P = A \cdot B \cdot C$$

## **LOGIC DIAGRAM:**

### **EVEN PARITY CHECKER:**

### **TRUTH TABLE:**

|   | INPUT |   |      |   |  |

|---|-------|---|------|---|--|

| A | В     | C | D(P) | P |  |

| 0 | 0     | 0 | 0    | 0 |  |

| 0 | 0     | 0 | 1    | 1 |  |

| 0 | 0     | 1 | 0    | 1 |  |

| 0 | 0     | 1 | 1    | 0 |  |

| 0 | 1     | 0 | 0    | 1 |  |

| 0 | 1     | 0 | 1    | 0 |  |

| 0 | 1     | 1 | 0    | 0 |  |

| 0 | 1     | 1 | 1    | 1 |  |

| 1 | 0     | 0 | 0    | 1 |  |

| 1 | 0     | 0 | 1    | 0 |  |

| 1 | 0     | 1 | 0    | 0 |  |

| 1 | 0     | 1 | 1    | 1 |  |

| 1 | 1     | 0 | 0    | 0 |  |

| 1 | 1     | 0 | 1    | 1 |  |

| 1 | 1     | 1 | 0    | 1 |  |

| 1 | 1     | 1 | 1    | 0 |  |

### K-MAP: EVEN PARITY CHECKER

| AB | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| 00 |    |    |    |    |

| 01 |    |    |    |    |

| 11 |    |    |    |    |

| 10 |    |    |    |    |

$P = A \cdot B \cdot C \cdot D$

### **LOGIC DIAGRAM**

## **VIVA QUESTIONS:**

- 1. What is parity bit?

- 2. What is a parity generator?

- 3. What is a parity checkers?

- 4. What is odd parity and even parity?

- 5. Why parity bit is added to message?

### **POST-LAB QUESTION:**

| 1. While using even parity, where is the parity bit placed?                                              |                              |  |  |  |

|----------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|

| a). Before the MSB                                                                                       | b). After the LSB            |  |  |  |

| b). In the parity word                                                                                   | d). After the odd parity bit |  |  |  |

| 2. If odd parity is used for ASCII error detection, the number of 0s per 8-bit symbol is                 |                              |  |  |  |

| a). Even                                                                                                 | b). Odd                      |  |  |  |

| c). Indeterminate                                                                                        | d). 42                       |  |  |  |

| 3. What VHDL techniques are used to describe a priority encoder? a). Integer outputs and priority coding |                              |  |  |  |

| b). Signal outputs and priority coding                                                                   |                              |  |  |  |

4. Solving -11 + (-2) will yield which two's-complement answer?

c). Tristate outputs and priority codingd). Variables and priority coding

a). 1110 1101

b). 1111 1001

c). 1111 0011

- d). 1110 1001

- 5. The most commonly used system for representing signed binary numbers is the:

- a). 2's-complement system.

- b). 1's-complement system.

- c) 10's-complement system.

- d). sign-magnitude system.

#### **RESULT:**

Thus the logic circuits are constructed and truth tables are verified for:

- (a) Odd Parity Generator

- (b) Odd Parity Checker

- (c) Even Parity Generator

- (d) Even Parity Checker

| Ex. No. 4 | ENCODERS AND DECODERS |

|-----------|-----------------------|

| Date:     | ENGODERO MAD DEGODERO |

#### **INTRODUCTION:**

#### **ENCODER:**

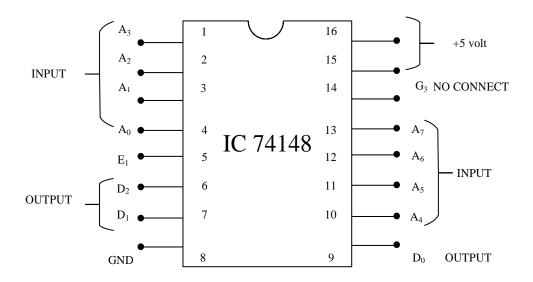

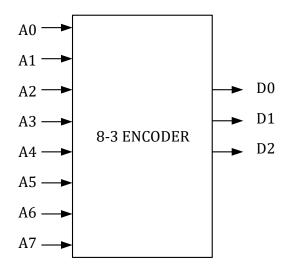

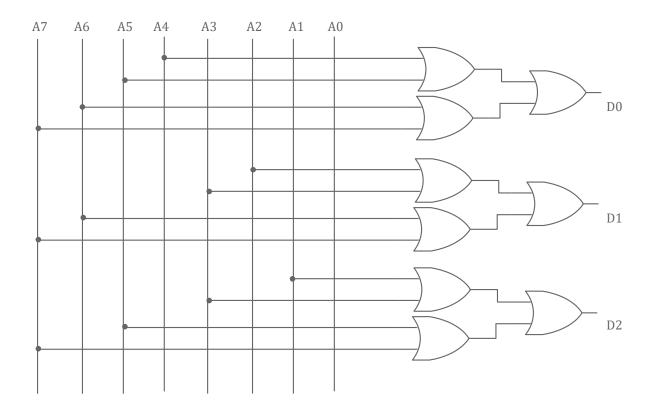

An encoder is digital circuit that has 2n input lines and n output lines. The output lines generate a binary code corresponding to the input values 8 - 3 encoder circuit has 8 inputs, one for each of the octal digits and three outputs that generate the corresponding binary number. Enable inputs E1 should be connected to ground and Eo should be connected to VCC.

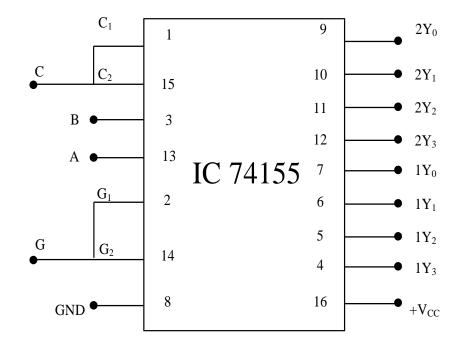

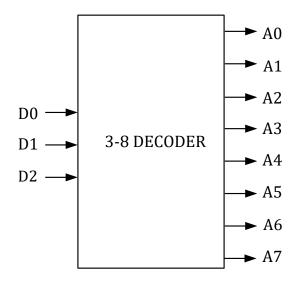

#### **DECODER:**

A decoder is a combinational circuit that converts binary information from n input lines to 2n unique output lines. In 3-8 line decoder the three inputs are decoded into right outputs in which each output representing one of the minterm of 3 input variables.

#### ANNA UNIVERSITY QUESTIONS

- 1. Design and implement encoder using suitable IC. Verify its truth table. (100)

- 2. Design and implement BCD 7 segment display decoder using suitable IC. (100)

- 3. Design and implement 2x4 decoder using suitable logic gates and verify its truth table.

(50)

4. Design and implement 4x2 encoder using suitable logic gates and verify its truth table.

(50)

5. Design and construct BCD to 7 segment display decoder using dedicated decoder IC. (100)

#### AIM:

- a) To design and implement encoder using IC 74148 (8-3 encoder)

- b) To design and implement decoder using IC 74155 (3-8 decoder)

TRUTH TABLE - ENCODERS

|                | INPUTS         |                |                       |                |            | О              | UTPUT          | ΓS             |   |                |

|----------------|----------------|----------------|-----------------------|----------------|------------|----------------|----------------|----------------|---|----------------|

| A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | A <sub>4</sub> | <b>A</b> 5 | A <sub>6</sub> | A <sub>7</sub> | $\mathbf{D_0}$ | D | $\mathbf{D_2}$ |

| 1              | 0              | 0              | 0                     | 0              | 0          | 0              | 0              | 0              | 0 | 0              |

| 0              | 1              | 0              | 0                     | 0              | 0          | 0              | 0              | 0              | 0 | 1              |

| 0              | 0              | 1              | 0                     | 0              | 0          | 0              | 0              | 0              | 1 | 0              |

| 0              | 0              | 0              | 1                     | 0              | 0          | 0              | 0              | 0              | 1 | 1              |

| 0              | 0              | 0              | 0                     | 1              | 0          | 0              | 0              | 1              | 0 | 0              |

| 0              | 0              | 0              | 0                     | 0              | 1          | 0              | 0              | 1              | 0 | 1              |

| 0              | 0              | 0              | 0                     | 0              | 0          | 1              | 0              | 1              | 1 | 0              |

| 0              | 0              | 0              | 0                     | 0              | 0          | 0              | 1              | 1              | 1 | 1              |

| 0              | 0              | 0              | 0                     | 0              | 0          | 0              | 0              | 1              | 1 | 1              |

# PIN DIAGRAM: ENCODER

## **BLOCK DIAGRAM OF 8-3 ENCODER:**

### **CIRCUIT DIAGRAM OF 8-3 ENCODER:**

### **PRE-LAB QUESTIONS:**

a). Encoder b). Display c). Counter d). Decoder 2. A principle regarding most IC decoders is that when the correct input is present, the related output will switch: a). Active -high b). To a high impedance d). Active -low c). To an open 3. How many possible outputs would a decoder have with a 6-bit binary input? b). 32 a). 16 c). 64 d). 128 4. How many inputs are required for a 1-of-16 decoder? b). 4 a). 2 c). 8 d). 16 5. If two inputs are active on a priority encoder, which will be coded on the output?

1. Which digital system translates coded characters into a more useful form?

### **APPARATUS REQUIRED:**

a). the higher value

c). neither of the inputs

| S.No | Components             | Specification | Quantity    |

|------|------------------------|---------------|-------------|

| 1    | Encoder                | IC 74148      | 1           |

| 2    | Decoder                | IC 74155      | 1           |

| 3    | OR gate                | IC 7432       | 3           |

| 4    | AND gate               | IC 7408       | 5           |

| 5    | NOT gate               | IC 7404       | 1           |

| 6    | Digital IC Trainer Kit | -             | 1           |

| 7    | Patch chords           | -             | As required |

b). The lower value

d). Both of the inputs

#### **PROCEDURE:**

- · Connections are given as per the logic diagram.

- The truth table is verified by varying the inputs.

### TRUTH TABLE - DECODERS:

| IN         | NPUTS      |    | OUTPUTS |           |    |    |    |    |    |    |

|------------|------------|----|---------|-----------|----|----|----|----|----|----|

| <b>D</b> 0 | <b>D</b> 1 | D2 | A7      | <b>A6</b> | A5 | A4 | A3 | A2 | A1 | A0 |

| 0          | 0          | 0  | 0       | 0         | 0  | 0  | 0  | 0  | 0  | 1  |

| 0          | 0          | 1  | 0       | 0         | 0  | 0  | 0  | 0  | 1  | 0  |

| 0          | 1          | 0  | 0       | 0         | 0  | 0  | 0  | 1  | 0  | 0  |

| 0          | 1          | 1  | 0       | 0         | 0  | 0  | 1  | 0  | 0  | 0  |

| 1          | 0          | 0  | 0       | 0         | 0  | 1  | 0  | 0  | 0  | 0  |

| 1          | 0          | 1  | 0       | 0         | 1  | 0  | 0  | 0  | 0  | 0  |

| 1          | 1          | 0  | 0       | 1         | 0  | 0  | 0  | 0  | 0  | 0  |

| 1          | 1          | 1  | 1       | 0         | 0  | 0  | 0  | 0  | 0  | 0  |

### PIN DIAGRAM: DECODER

## **BLOCK DIAGRAM OF 3-8 DECODER**

### **CIRCUIT DIAGRAM OF 3-8 DECODER**

# **VIVA QUESTIONS:**

- 1. What do you mean by encoder?

- 2. What is a priority encoder?

- 3. What are the applications of decoders?

- 4. Distinguish between a demultiplexer and decoder

- 5. List the types of decoder ICs.

#### P

|      | 71              |                       |                     |                |                |         |

|------|-----------------|-----------------------|---------------------|----------------|----------------|---------|

| POST | T-LAB QUES      | TIONS:                |                     |                |                |         |

| 1.   | How many o      | outputs are on a BCI  | O decoder?          |                |                |         |

|      | A.              | 4                     | В.                  | 16             |                |         |

|      | C.              | 8                     | D.                  | 10             |                |         |

| 2.   | In a Gray of    | code, each number     | is 3 greater that   | n the binary   | representation | of that |

|      | number.         |                       |                     |                |                |         |

|      | A.              | True                  | В.                  | False          |                |         |

| 3. V | Which digital s | system translates co  | ded characters into | a more usefu   | ıl form?       |         |

|      | A.              | encoder               | В.                  | Display        |                |         |

|      | C.              | counters              | D.                  | Decoder        |                |         |

| 4.   | How many is     | nputs are required fe | or a 1-of-10 BCD    | decoder?       |                |         |

|      | A.              | 4                     | В.                  | 8              |                |         |

|      | C.              | 10                    | D.                  | 1              |                |         |

| 5. V | When two or m   | nore inputs are activ | e simultaneously,   | the process is | called:        |         |

|      | A.              | First-in, first-out   | processing          |                |                |         |

|      | B.              | priority encoding     |                     |                |                |         |

|      | C.              | ripple blanking       |                     |                |                |         |

|      | D.              | First-in, first-out   | processing or prio  | rity encoding  |                |         |

|      |                 |                       |                     |                |                |         |

|      |                 |                       |                     |                |                |         |

### **RESULT:**

Thus the logic diagrams were constructed and the truth tables are verified for 8 to 3 line Encoder and 3 to 8 line Decoder.

| Ex. No. 5 | COUNTERS |

|-----------|----------|

| Date:     |          |

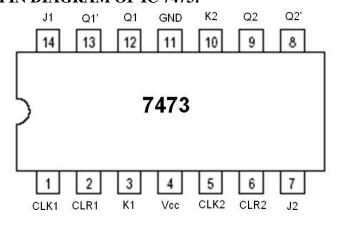

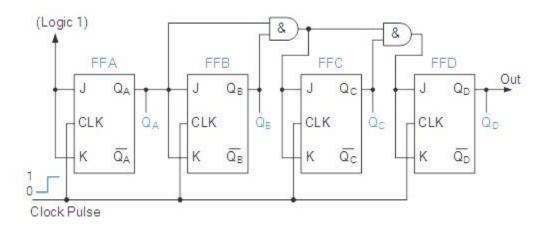

A counter is a register capable of counting number of clock pulse arriving at its clock input. Counter represents the number of clock pulses arrived. An up/down counter is one that is capable of progressing in increasing order or decreasing order through a certain sequence. An up/down counter is also called bidirectional counter. Usually up/down operation of the counter is controlled by up/down signal. When this signal is high counter goes through up sequence and when up/down signal is low counter follows reverse sequence.

#### **ANNA UNIVERSITY QUESTIONS:**

- 1. Design an asynchronous/ripple 4-bit binary up counter using JK flip flops.

- 2. Design an asynchronous/ripple 4-bit binary down counter using JK flip flops.

- 3. Design an asynchronous/ripple 4-bit decimal (BCD) up counter using JK flip flops.

- 4. Design an asynchronous/ripple 4-bit decimal (BCD down counter using JK flip flops.

- 5. Design a 4 bit synchronous binary up counter using JK flip flops.

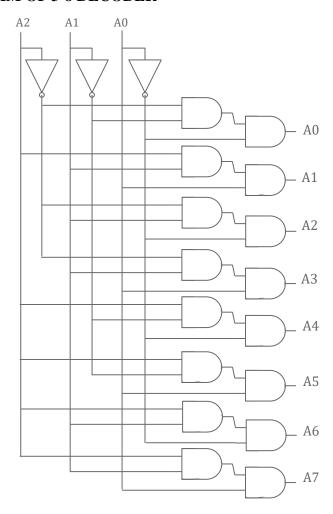

#### **PIN DIAGRAM OF IC 7473:**

## **CIRCUIT DIAGRAM (ASYNCHRONOUS COUNTER):**

| TRUTH TAB | LE: |            |                 |              |         |

|-----------|-----|------------|-----------------|--------------|---------|

| Clock     |     | Output     |                 |              | Decimal |

| Count     | QD  | <b>Q</b> c | QB              | QA           | Value   |

| 1         | 0   | 0          | 0               | 0            | 0       |

| 2         | 0   | 0          | 0               | 1            | 1       |

| 3         | 0   | 0          | 1               | 0            | 2       |

| 4         | 0   | 0          | 1               | 1            | 3       |

| 5         | 0   | 1          | 0               | 0            | 4       |

| 6         | 0   | 1          | 0               | 1            | 5       |

| 7         | 0   | 1          | 1               | 0            | 6       |

| 8         | 0   | 1          | 1               | 1            | 7       |

| 9         | 1   | 0          | 0               | 0            | 8       |

| 10        | 1   | 0          | 0               | 1            | 9       |

| 11        |     | Counter Re | sets its output | back to zero |         |

### AIM:

To implement and verify the truth table of synchronous and asynchronous counter.

# **APPARATUS REQUIRED:**

| S. No | Components             | Range   | Quantity    |

|-------|------------------------|---------|-------------|

| 1.    | Digital IC trainer kit |         | 1           |

| 2.    | JK Flip Flop           | IC 7473 | 2           |

| 4.    | NAND gate              | IC 7400 | 1           |

| 5.    | AND gate               | IC 7408 | 1           |

| 6.    | Connecting wires       |         | As required |

### **PROCEDURE:**

- · Connections are given as per the logic diagram.

- The truth table is verified by varying the inputs.

# CIRCUIT DIAGRAM (ASYNCHRONOUS COUNTER):

**TRUTH TABLE:**

| Clock |    |                           | Decimal        |                           |       |

|-------|----|---------------------------|----------------|---------------------------|-------|

| Count | QD | $\mathbf{Q}_{\mathbf{C}}$ | Q <sub>B</sub> | $\mathbf{Q}_{\mathbf{A}}$ | Value |

|       |    |                           |                | _                         |       |

| 1     | 0  | 0                         | 0              | 0                         | 0     |

| 2     | 0  | 0                         | 0              | 1                         | 1     |

| 3     | 0  | 0                         | 1              | 0                         | 2     |

| 4     | 0  | 0                         | 1              | 1                         | 3     |

| 5     | 0  | 1                         | 0              | 0                         | 4     |

| 6     | 0  | 1                         | 0              | 1                         | 5     |

| 7     | 0  | 1                         | 1              | 0                         | 6     |

| 8     | 0  | 1                         | 1              | 1                         | 7     |

| 9     | 1  | 0                         | 0              | 0                         | 8     |

| 10    | 1  | 0                         | 0              | 1                         | 9     |

| 11    | 1  | 0                         | 1              | 0                         | 10    |

| 12    | 1  | 0                         | 1              | 1                         | 11    |

| 13    | 1  | 1                         | 0              | 0                         | 12    |

| 14    | 1  | 1                         | 0              | 1                         | 13    |

| 15    | 1  | 1                         | 1              | 0                         | 14    |

| 16    | 1  | 1                         | 1              | 1                         | 15    |

Decl7de Counter Timing Di Counter Resets its output back to zero

| 1.       | Define clock.                           |                                                   |

|----------|-----------------------------------------|---------------------------------------------------|

|          | Define clock period.                    |                                                   |

|          | What is flip-flop?                      |                                                   |

| 4.<br>5. |                                         |                                                   |

|          | LAB QUESTIONS:                          |                                                   |

|          | The terminal count of a modulus-11      | binary counter is                                 |

|          | a). 1010                                | b). 1000                                          |

|          | c). 1001                                | d). 1100                                          |

| 2.       | Synchronous construction reduces th     | e delay time of a counter to the delay of:        |

|          | a). All flip-flops & gates              | b). All flip-flops and gates a 3 count            |

|          | c). A single gate                       | d). A single flip-flop & a gate                   |

| 3.       | A BCD counter is a                      |                                                   |

|          | a). binary counter                      | b). Full-modulus counter                          |

|          | c). decade counter                      | d). divide-by-10 counter                          |

| 4.       | How many different states does a 3-b    | oit asynchronous counter have?                    |

|          | a). 2                                   | b). 4                                             |

|          | c). 8                                   | d). 16                                            |

| 5.       | The final output of a modulus-8 cour    | nter occurs one time for every                    |

|          | a). 8 clock pulses                      | b). 16 clock pulses                               |

|          | c). 24 clock pulses                     | d). 32 clock pulses                               |

| POST     | -LAB QUESTION:                          |                                                   |

| 1.       | If both inputs of a gated S-R flip-flor | o are LOW, what will happen when the flip-flop is |

|          | enabled?                                |                                                   |

|          | a). No change will occur in the outp    | ut b). An invalid state will exist                |

|          | c). The output will toggle.             | d). The output will reset.                        |

|          | , 1                                     | , 1                                               |

| 2.       | The parallel outputs of a counter circ  | uit represent the:                                |

|          | a). parallel data word                  | b). clock frequency                               |

|          | c). counter modulus                     | d). clock count                                   |

| 3.       | The One example of the use of an S-     | R flip-flop is as a(n):                           |

|          | a). racer                               |                                                   |

|          | b). astable oscillator                  |                                                   |

|          | c). binary storage register             |                                                   |

|          | , , , , , , , , , , , , , , , , , , , , |                                                   |

**VIVA QUESTIONS:**

- d). transition pulse generator

- 4. One of the major drawbacks to the use of asynchronous counters is:

- a). low-frequency applications are limited because of internal propagation delays

- b). high-frequency applications are limited because of internal propagation delays

- c). asynchronous counters do not have major drawbacks and are suitable for use in high- and low-frequency counting applications

- d). asynchronous counters do not have propagation delays and this limits their use in high-frequency applications

- 5. Synchronous counters eliminate the delay problems encountered with asynchronous counters because the:

- a). input clock pulses are applied only to the first and last stages

- b). input clock pulses are applied only to the last stage

- c). input clock pulses are not used to activate any of the counter stages

- d). input clock pulses are applied simultaneously to each stage

#### **RESULT:**

The truth table of Asynchronous counter and Synchronous counter was verified.

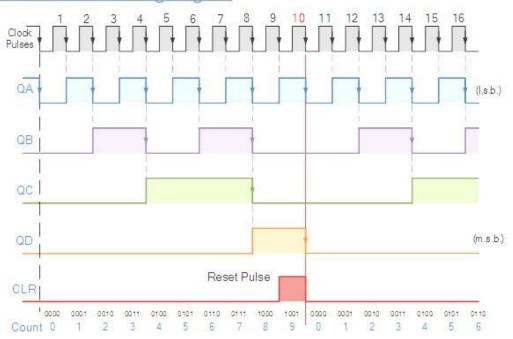

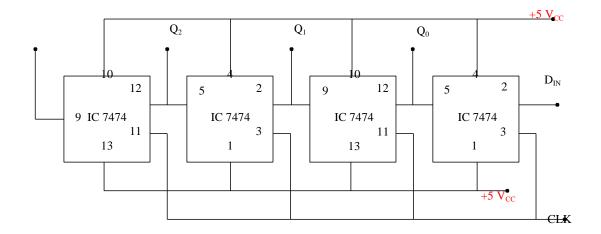

| Ex. No. 6 Date: | SHIFT REGISTERS |

|-----------------|-----------------|

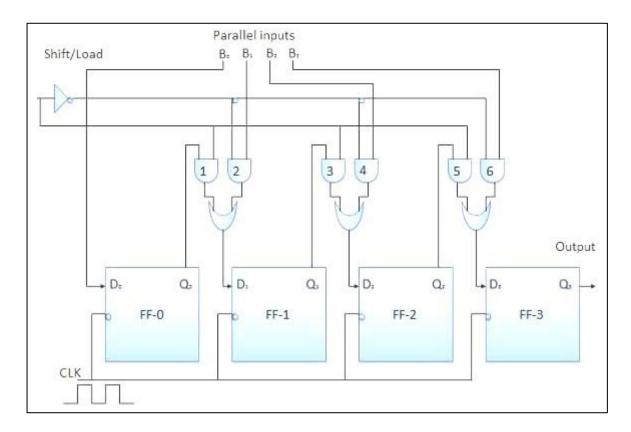

The Shift Register is another type of sequential logic circuit that can be used for the storage or the transfer of data in the form of binary numbers. This sequential device loads the data present on its inputs and then moves or "shifts" it to its output once every clock cycle, hence the name "shift register". A register capable of shifting its binary information either to the left or to the right is called a shift register. The logical configuration of a shift register consists of a chain of flip flops connected in cascade with the output of one flip flop connected to the input of the next flip flop. All the flip flops receive a common clock pulse which causes the shift from one stage to the next.

#### ANNA UNIVERSITY QUESTIONS

- Design and construct a 4-bit shift register in SISO, SIPO, PISO and PIPO modes using suitable ICs.

(100)

- 2. Design & construct a 4 bit Serial in serial out shift register. (100)

- 3. Design & construct a 4 bit Serial in parallel out shift register. (100)

- 4. Design & construct a 4 bit Parallel in serial out shift register. (100)

- 5. Design & construct a 4 bit Parallel in parallel out shift register. (100)

#### AIM:

To implement the following shift register using flip flop

(i) SIPO (ii) SISO (iii) PISO (iv) PIPO

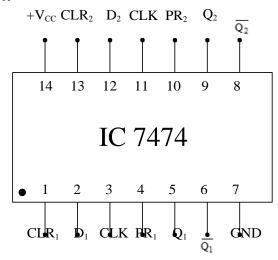

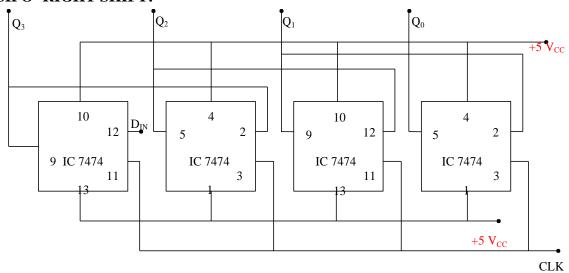

#### **PIN DIAGRAM IC7474:**

# **SIPO-LEFT SHIFT:**

# **APPARATUS REQUIRED:**

| S. No | Component              | Specification | Quantity |

|-------|------------------------|---------------|----------|

| 1.    | IC .                   | 7474          | 1        |

| 2.    | Digital IC Trainer Kit |               | 1        |

| 3.    | Patch chords           |               | _        |

### **PROCEDURE:**

- Give the connections as per the circuit.

- · Set or Reset at pin no:2 which is the MSB of serial data

- · Apply a single clock Set or Reset second digital input at pin no:2.

- · Repeat step 2 until all 4-bit data are taken away.

### **VERIFICATION TABLE:**

| No of clock | Serial input D <sub>in</sub> | Parallel output |       |    |    |

|-------------|------------------------------|-----------------|-------|----|----|

| pulse       |                              | <b>Q</b> 3      | $Q_2$ | Qı | Qo |

| 0           | 0                            | 0               | 0     | 0  | 0  |

| 1           | 1                            | 0               | 0     | 0  | 1  |

| 2           | 1                            | 0               | 0     | 1  | 1  |

| 3 | 0 | 0 | 1 | 1 | 0 |

|---|---|---|---|---|---|

| 4 | 1 | 1 | 1 | 0 | 1 |

| 5 | 0 | 1 | 0 | 1 | 0 |

| 6 | 0 | 0 | 1 | 0 | 0 |

| 7 | 0 | 1 | 0 | 0 | 0 |

| 8 | 0 | 0 | 0 | 0 | 0 |

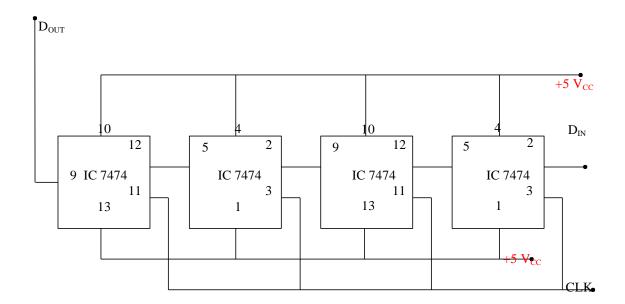

SIPO- RIGHT SHIFT:

# **VERIFICATION TABLE:**

| No of clock pulse | Serial input D <sub>in</sub> | Parallel output |                |       |       |

|-------------------|------------------------------|-----------------|----------------|-------|-------|

|                   |                              | Q <sub>3</sub>  | Q <sub>2</sub> | $Q_1$ | $Q_0$ |

| 0                 | 0                            | 0               | 0              | 0     | 0     |

| 1                 | 1                            | 1               | 0              | 0     | 0     |

| 2                 | 1                            | 0               | 1              | 0     | 0     |

| 3                 | 0                            | 1               | 0              | 1     | 0     |

| 4                 | 1                            | 1               | 1              | 0     | 1     |

| 5                 | 0                            | 0               | 1              | 1     | 0     |

| 6                 | 0                            | 0               | 0              | 1     | 1     |

| 7                 | 0                            | 0               | 0              | 0     | 1     |

| 8                 | 0                            | 0               | 0              | 0     | 0     |

## SISO:

# **VERIFICATION TABLE:**

Data input = 1100

| Clock | Serial input | Serial output |

|-------|--------------|---------------|

| 0     | 0            | 0             |

| 4     | 1            | 1             |

| 8     | 1            | 1             |

| 12    | 0            | 0             |

| 16    | 0            | 0             |

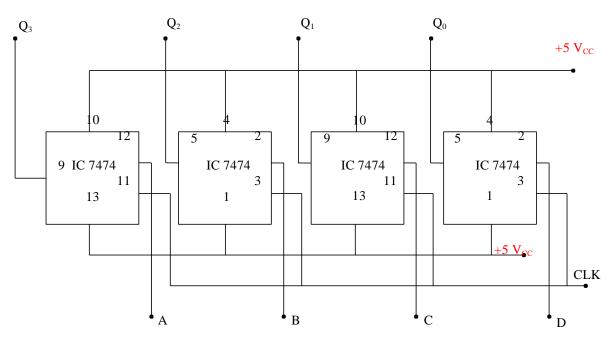

# PIPO:

# **VERIFICATION TABLE:**

| Clock | Parallel input |   |   |   | Parallel output |    |    |    |

|-------|----------------|---|---|---|-----------------|----|----|----|

|       | A              | В | С | D | QA              | QB | Qc | QD |

| 0     | 0              | 0 | 0 | 0 | 0               | 0  | 0  | 0  |

| 1     | 1              | 1 | 0 | 1 | 1               | 1  | 0  | 1  |

# **PISO:**

| PRE-LAB ( | QUESTI | ONS: |

|-----------|--------|------|

|-----------|--------|------|

| 1.       | How is a shift register that                                      | will accept a parallel input, or a bidirectional serial load         |  |  |  |  |  |

|----------|-------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

|          | and internal shift features, ca                                   | alled?                                                               |  |  |  |  |  |

|          | a). Tristate                                                      | b). End around                                                       |  |  |  |  |  |

|          | c). Universal                                                     | d). Conversion                                                       |  |  |  |  |  |

| 2.       | How much storage capacity                                         | much storage capacity does each stage in a shift register represent? |  |  |  |  |  |

|          | a). One bit                                                       | b). Two bits                                                         |  |  |  |  |  |

|          | c). Four bits                                                     | d). Eight bits                                                       |  |  |  |  |  |

| 3.       | Which is not the characteristic of a shift register?              |                                                                      |  |  |  |  |  |

|          | a). Serial in/parallel in                                         | b). Serial in/parallel out                                           |  |  |  |  |  |

|          | c). Parallel in/serial out                                        | d). Parallel in/parallel out                                         |  |  |  |  |  |

| 4.       | 4. A 74HC195 4-bit parallel access shift register can be used for |                                                                      |  |  |  |  |  |

|          | a). serial in/serial out opera-                                   | tion b). Serial in/parallel out operation                            |  |  |  |  |  |

|          | c). parallel in/serial out oper                                   | ation d). All of the above                                           |  |  |  |  |  |

| 5.       | vill be required to completely load serially a 5-bit              |                                                                      |  |  |  |  |  |

|          | shift register?                                                   |                                                                      |  |  |  |  |  |

|          | a). 2                                                             | b). 3                                                                |  |  |  |  |  |

|          | c). 4                                                             | d). 5                                                                |  |  |  |  |  |

|          |                                                                   |                                                                      |  |  |  |  |  |

|          |                                                                   |                                                                      |  |  |  |  |  |

| VIVA     | QUESTIONS:                                                        |                                                                      |  |  |  |  |  |

| 1.       | Define shift register.                                            |                                                                      |  |  |  |  |  |

| 2.       | What are the different types                                      | of shift registers?                                                  |  |  |  |  |  |

| 3.       | Mention the applications of shift registers.                      |                                                                      |  |  |  |  |  |

| 4.       | What is a register?                                               |                                                                      |  |  |  |  |  |

| 3.       | What is shift register counte                                     | 1 !                                                                  |  |  |  |  |  |

| POST     | -LAB QUESTIONS:                                                   |                                                                      |  |  |  |  |  |

| 1.       | Another way to connect dev                                        | ices to a shared data bus is to use a                                |  |  |  |  |  |

|          | a). circulating gate                                              | b). Transceiver                                                      |  |  |  |  |  |

|          | c). bidirectional encoder                                         | d). strobed latch                                                    |  |  |  |  |  |

| 2.<br>by | _                                                                 | receives 4 bits of parallel data will shift to the                   |  |  |  |  |  |

| ,        | position(s) for each c                                            | lock pulse.                                                          |  |  |  |  |  |

|          | a). right, one                                                    | b). right, two                                                       |  |  |  |  |  |

|          | c). left, one                                                     | d). left, three                                                      |  |  |  |  |  |

| 3. | Computers operate on data in      | ternally in a format.                                         |

|----|-----------------------------------|---------------------------------------------------------------|

|    | a). tristate                      | b). universal                                                 |

|    | c). parallel                      | d). serial                                                    |

| 4. | By adding recirculating lines     | to a 4-bit parallel-in, serial-out shift register, it becomes |

|    | a, ando                           | ut register.                                                  |

|    | a). parallel-in, serial, parallel | b). serial-in, parallel, serial                               |

|    | c). series-parallel-in, series, p | arallel d). bidirectional in, parallel, series                |

| 5. | One purpose of a three-state l    | ouffer is:                                                    |

|    | a). to provide isolation between  | een the input device and the data bus                         |

|    | b). to provide the sink or sour   | rce current required by any device connected to its output    |

|    | without loading down the out      | put device                                                    |

|    | c). temporary data storage        |                                                               |

|    | d). to control data flow          |                                                               |

# **RESULT:**

Thus the SISO, SIPO, PISO, PIPO shift registers were designed and implemented.

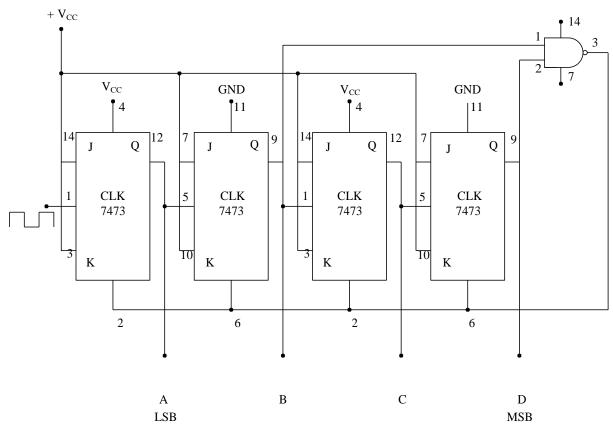

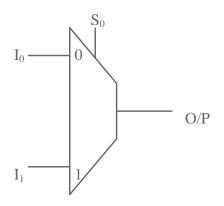

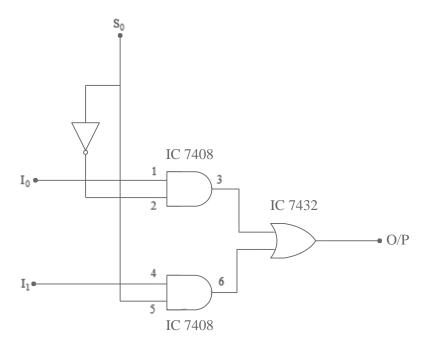

# a) 2: 1 MULTIPLEXER:

| So | O/P   |

|----|-------|

| 0  | $I_0$ |

| 1  | $I_1$ |

|    |       |

# **LOGIC DIAGRAM:**

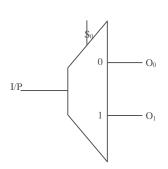

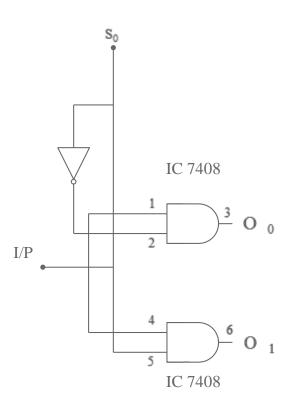

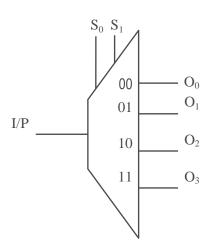

# b) 1: 2 DE MULTIPLEXER:

| $O_0$ |

|-------|

| $O_1$ |

|       |

| Ex. No. 7 | MULTIPLEXER AND DEMULTIPLEXER |

|-----------|-------------------------------|

| Date:     |                               |

#### **INTRODUCTION:**

Multiplexer is a digital switch which allows digital information from several sources to be routed onto a single output line. The basic multiplexer has several data input lines and a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally, there are 2n input lines and n selector lines whose bit combinations determine which input is selected. Therefore, multiplexer is 'many into one' and it provides the digital equivalent of an analog selector switch.

A Demultiplexer is a circuit that receives information on a single line and transmits this information on one of 2n possible output lines. The selection of specific output line is controlled by the values of n selection lines.

### **ANNA UNIVERSITY QUESTIONS:**

- 1. Design & implement 1x4 demultiplexer by using suitable logic gates & verify its truth table (100)

- 2. Design & implement 4x1 Multiplexer by using suitable logic gates & verify its truth table (100)

- 3. Design 1:4 de multiplexer using suitable ICs. (100)

- 4. Design 4:1 multiplexer using suitable ICs. (100)

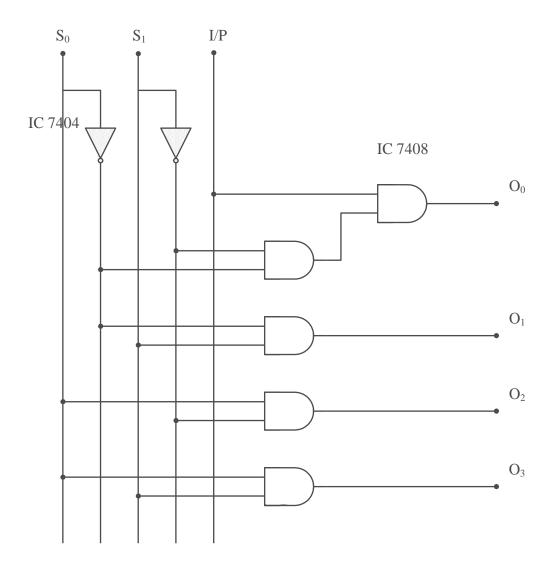

#### AIM:

To construct the logic diagram and verify the truth table for:

- (a) 2:1 Multiplexer

- (b) 1: 2 De multiplexer

- (c) 4:1 Multiplexer.

- (d) 1: 4 De multiplexer.

# **LOGIC DIAGRAM:**

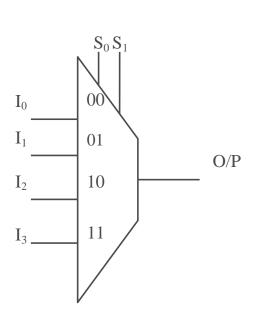

# a) 4: 1 MULTIPLEXER:

| $S_0$ | $S_1$  | O/P                                    |

|-------|--------|----------------------------------------|

|       |        |                                        |

| 0 0   | 0<br>1 | $egin{array}{c} I_0 \ I_1 \end{array}$ |

| 1     | 0      | $I_2$                                  |

| 1     | 1      | $I_3$                                  |

|       |        |                                        |

### **PRE-LAB QUESTIONS:**

1. What is the function of an enable input on a multiplexer chip?

a). To apply Vcc

b). To connect ground

c). To active the entire chip

d). To active one half of the chip

2. A basic multiplexer principle can be demonstrated through the use of a:

a). Single pole relay

b). DPDT switch

c). Rotary switch

d). Linear stepper

3. Most de multiplexers facilitate which type of conversion?

a). Decimal-Hex

b). Single input, multiple outputs

c). AC-DC

d). Odd parity to Even parity

4. The inputs/outputs of an analog multiplexer/demultiplexer are:

a). bidirectional

b). Unidirectional

c). even parity

d). Binary-coded decimal

5. One application of a digital multiplexer is to facilitate:

a). data generation

b). Serial-to-parallel conversion

c). parity checking

d). Data selector

### **APPARATUS REQUIRED:**

| Sl.No | Component                | Specification | Quantity    |

|-------|--------------------------|---------------|-------------|

| 1     | X-OR Gate                | IC 7486       | 1           |

| 2     | NOT Gate                 | IC 7404       | 1           |

| 3     | AND Gate                 | IC 7408       | 1           |

| 4     | OR Gate                  | IC 7432       | 1           |

| 5     | IC TRAINER KIT           | -             | 1           |